## 54F/74F181 4-Bit Arithmetic Logic Unit

### **General Description**

The 'F181 is a 4-bit Arithmetic logic Unit (ALU) which can perform all the possible 16 logic operations on two variables and a variety of arithmetic operations. It is 40% faster than the Schottky ALU and only consumes 30% as much power.

### **Features**

- Full lookahead for high-speed arithmetic operation on long words

- Guaranteed 4000V minimum ESD protection

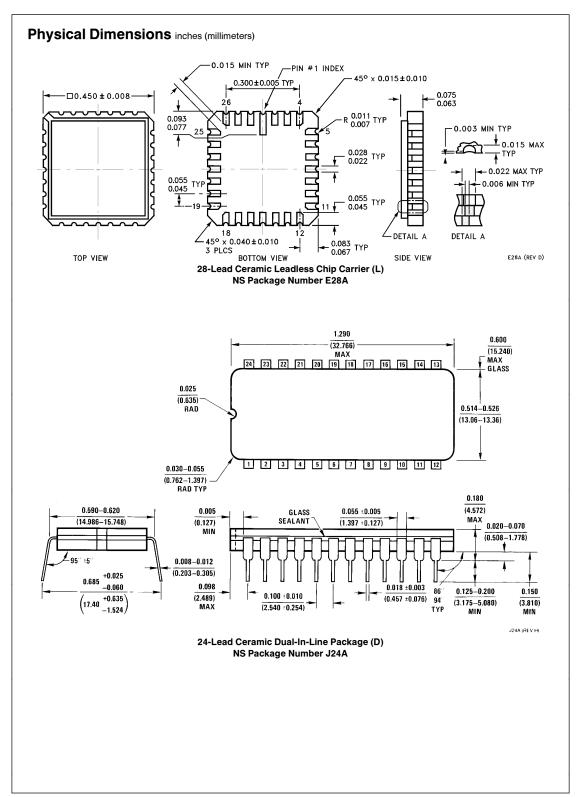

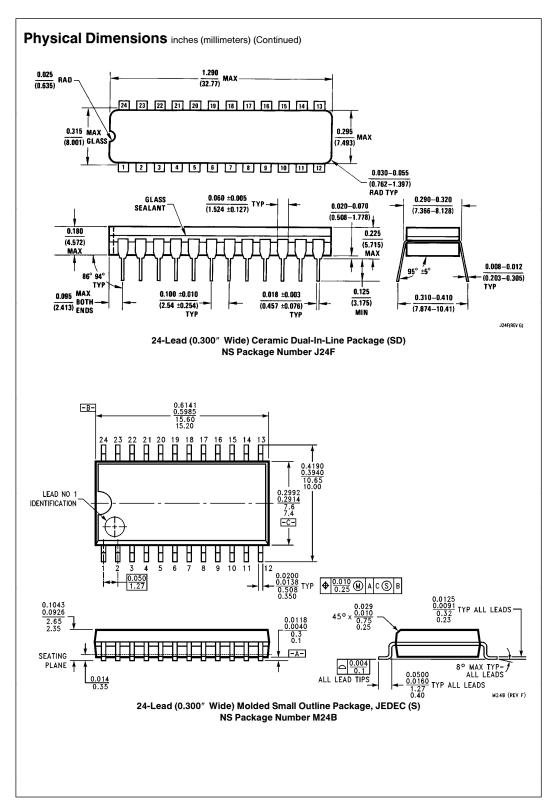

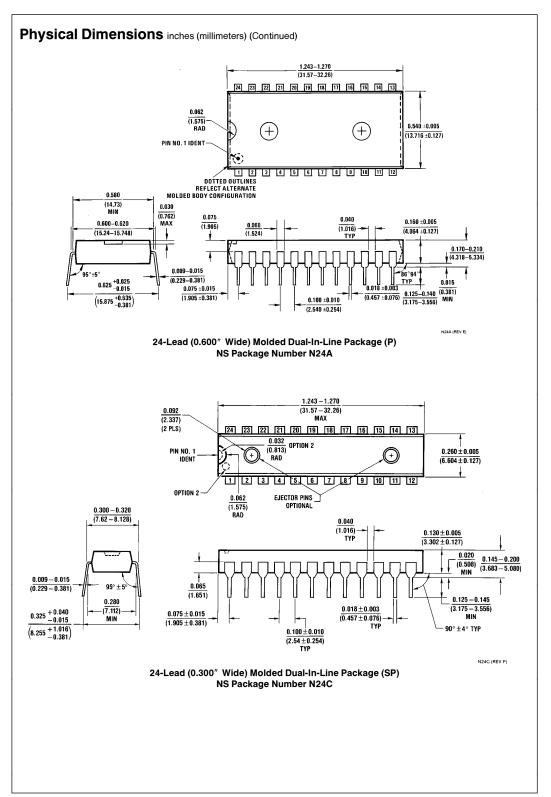

| Commercial        | Military           | Package<br>Number | Package Description                           |  |  |  |  |

|-------------------|--------------------|-------------------|-----------------------------------------------|--|--|--|--|

| 74F181PC          |                    | N24A              | 24-Lead (0.600" Wide) Molded Dual-In-Line     |  |  |  |  |

| 74F181SPC         |                    | N24C              | 24-Lead (0.300" Wide) Molded Dual-In-Line     |  |  |  |  |

|                   | 54F181DM (Note 2)  | J24A              | 24-Lead Ceramic Dual-In-Line                  |  |  |  |  |

|                   | 54F181SDM (Note 2) | J24F              | 24-Lead (0.300") Ceramic Dual-In-Line         |  |  |  |  |

| 74F181SC (Note 1) |                    | M24B              | 24-Lead (0.300") Molded Small Outline, JEDEC  |  |  |  |  |

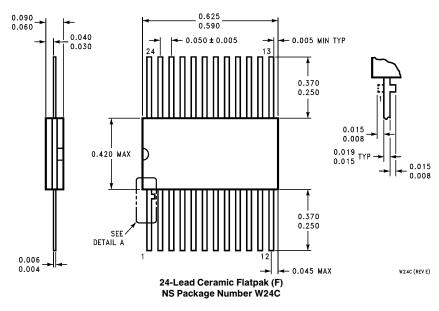

|                   | 54F181FM (Note 2)  | W24C              | 24-Lead Cerpack                               |  |  |  |  |

|                   | 54F181LM (Note 2)  | E28A              | 24-Lead Ceramic Leadless Chip Carrier, Type C |  |  |  |  |

Note 1: Devices also available in 13" reel. Use suffix = SCX.

Note 2: Military grade device with environmental and burn-in processing. Use suffix = DMQB, FMQB and LMQB.

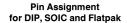

### **Connection Diagrams**

TL/F/9491-1

### Pin Assignment for LCC $\bar{F}_0$ M $C_n$ NC $S_0$ $S_1$ $S_2$

TL/F/9491-2

TRI-STATE® is a registered trademark of National Semiconductor Corporation

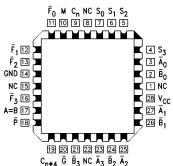

### **Logic Symbols**

# $\begin{array}{c} S_0 & & & & \\ S_1 & & & \\ S_2 & & & \\ S_2 & & & \\ S_3 & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\$

IEEE/IEC

### **Unit Loading/Fan Out**

|                                   |                                     | 54F/74F          |                                                                                   |  |  |  |

|-----------------------------------|-------------------------------------|------------------|-----------------------------------------------------------------------------------|--|--|--|

| Pin Names                         | Description                         | U.L.<br>HIGH/LOW | Input I <sub>IH</sub> /I <sub>IL</sub><br>Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |  |

| $\overline{A}_0 - \overline{A}_3$ | A Operand Inputs (Active LOW)       | 1.0/3.0          | 20 μA/ – 1.8 mA                                                                   |  |  |  |

| $\overline{B}_0 - \overline{B}_3$ | B Operand Inputs (Active LOW)       | 1.0/3.0          | 20 μA/ – 1.8 mA                                                                   |  |  |  |

| S <sub>0</sub> -S <sub>3</sub>    | Function Select Inputs              | 1.0/4.0          | 20 μA/ -2.4 mA                                                                    |  |  |  |

| М                                 | Mode Control Input                  | 1.0/1.0          | 20 μA/ -0.6 mA                                                                    |  |  |  |

| C <sub>n</sub>                    | Carry Input                         | 1.0/5.0          | 20 μA/ -3.0 mA                                                                    |  |  |  |

| $\overline{F}_0 - \overline{F}_3$ | Function Outputs (Active LOW)       | 50/33.3          | -1 mA/20 mA                                                                       |  |  |  |

| A = B                             | Comparator Output                   | OC*/33.3         | */20 mA                                                                           |  |  |  |

| G                                 | Carry Generate Output (Active LOW)  | 50/33.3          | -1 mA/20 mA                                                                       |  |  |  |

| P                                 | Carry Propagate Output (Active LOW) | 50/33.3          | -1 mA/20 mA                                                                       |  |  |  |

| $C_{n+4}$                         | Carry Output                        | 50/33.3          | -1 mA/20 mA                                                                       |  |  |  |

\*OC-Open Collector

### **Functional Description**

The 'F181 is a 4-bit high-speed parallel Arithmetic Logic Unit (ALU). Controlled by the four Function Select inputs  $(S_0-S_3)$  and the Mode Control input (M), it can perform all the 16 possible logic operations or 16 different arithmetic operations on Active HIGH or Active LOW operands. The Function Table lists these operations.

When the Mode Control input (M) is HIGH, all internal carries are inhibited and the device performs logic operations on the individual bits as listed. When the Mode Control input is LOW, the carries are enabled and the device performs arithmetic operations on the two 4-bit words. The device incorporates full internal carry lookahead and provides for either ripple carry between devices using the  $C_{n\,+\,4}$  output, or for carry lookahead between packages using the signals  $\overline{P}$  (Carry Propagate) and  $\overline{G}$  (Carry Generate). In the Add mode,  $\overline{P}$  indicates that  $\overline{F}$  is 15 or more, while  $\overline{G}$  indicates that  $\overline{F}$  is 16 or more. In the Subtract mode  $\overline{P}$  indicates that  $\overline{F}$ is zero or less, while  $\overline{G}$  indicates that  $\overline{F}$  is less than zero.  $\overline{P}$ and  $\overline{\mathbf{G}}$  are not affected by carry in. When speed requirements are not stringent, the 'F181 can be used in a simple Ripple Carry mode by connecting the Carry output (C<sub>n</sub>+4) signal to the Carry input (Cn) of the next unit. For high speed operation the device is used in conjunction with a carry lookahead circuit. One carry lookahead package is required for

each group of four 'F181 devices. Carry lookahead can be provided at various levels and offers high speed capability over extremely long word lengths.

The A = B output from the device goes HIGH when all four  $\overline{F}$  outputs are HIGH and can be used to indicate logic equivalence over four bits when the unit is in the Subtract mode. The A = B output is open collector and can be wired AND with other A = B outputs to give a comparison for more than four bits. The A = B signal can also be used with the  $C_{n+4}$  signal to indicate A>B and A<B.

The Function Table lists the arithmetic operations that are performed without a carry in. An incoming carry adds a one to each operation. Thus, select code LHHL generates A minus B minus 1 (2s complement notation) without a carry in and generates A minus B when a carry is applied. Because subtraction is actually performed by complementary addition (1s complement), a carry out means borrow; thus a carry is generated when there is no underflow and no carry is generated when there is underflow. As indicated, this device can be used with either active LOW inputs producing active LOW outputs or with active HIGH inputs producing active HIGH outputs. For either case the table lists the operations that are performed to the operands labeled inside the logic symbol.

| 'F181 Operation Table                                                                                                                                   |                |                |                |                |                               |                                                           |                                                               |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|-------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|--|--|--|

|                                                                                                                                                         | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | Logic<br>(M=H)                | Arithmetic $(M = L, C_0 = Inactive)$                      | Arithmetic<br>(M=L, C <sub>0</sub> = Active)                  |  |  |  |

|                                                                                                                                                         | L              | L              | L              | L              | Ā                             | A minus 1                                                 | A                                                             |  |  |  |

|                                                                                                                                                         | Н              | L              | L              | L              | Ā∙B                           | A ● B minus 1                                             | A●B                                                           |  |  |  |

| A B A B A B A B                                                                                                                                         | L              | Н              | L              | L              | Ā + B                         | A ● B minus 1                                             | A●B                                                           |  |  |  |

| C <sub>n</sub> ~0 50 ~1 51 ~2 52 ~3 53 C <sub>n+4</sub>                                                                                                 | H              | H              | L              | L              | Logic "1"                     | minus 1 (2s comp.)                                        | Zero                                                          |  |  |  |

| <b>⊣</b> м                                                                                                                                              | L              | L              | H<br>H         | L              | $\overline{A} + \overline{B}$ | A plus $(A + \overline{B})$                               | A plus (A + B) plus 1                                         |  |  |  |

| S <sub>0</sub> A=B                                                                                                                                      | H<br>L         | L<br>H         | Н              | L<br>L         | <u> </u>                      | A ● B plus (A + B̄) A minus B minus 1                     | A • B plus (A + B̄) plus<br>A minus B                         |  |  |  |

| <b>-</b>  s <sub>1</sub>                                                                                                                                | Н              | H              | н              | L              | $A + \overline{B}$            | $A + \overline{B}$                                        | A + B plus 1                                                  |  |  |  |

| $ s_2$                                                                                                                                                  | Ľ              | L              | L              | H              | Ā∙B                           | A plus (A + B)                                            | A plus (A + B plus 1                                          |  |  |  |

| S <sub>3</sub> F <sub>0</sub> F <sub>1</sub> F <sub>2</sub> F <sub>3</sub> P                                                                            | Н              | L              | L              | Н              | A⊕B                           | A plus B                                                  | A plus B plus 1                                               |  |  |  |

| <del>Ŏ</del> Ŏ Ŏ Ŏ                                                                                                                                      | L              | Н              | L              | Н              | В                             | A ● B plus (A + B)                                        | A • B plus (A + B) plus                                       |  |  |  |

| 1 1 1 1                                                                                                                                                 | Н              | Н              | L              | Н              | A + B                         | A + B                                                     | A + B plus 1                                                  |  |  |  |

| a. All Input Data Inverted                                                                                                                              | L              | L              | Н              | Н              | Logic "0"                     | A plus A (2 $\times$ A)                                   | A plus A (2 $\times$ A) plus 1                                |  |  |  |

|                                                                                                                                                         | Н              | L              | Н              | Н              | A●B                           | A plus A ● B                                              | A plus A • B plus 1                                           |  |  |  |

|                                                                                                                                                         | L              | H<br>H         | Н              | H<br>H         | A • B                         | A plus A ● B                                              | A plus A ● B plus 1                                           |  |  |  |

|                                                                                                                                                         | H<br>L         | <br>L          | H<br>L         | L              | A<br>Ā                        | A A                                                       | A plus 1                                                      |  |  |  |

|                                                                                                                                                         | Н              | L              | L              | L              | $\frac{A}{A+B}$               | A + B                                                     | A plus 1<br>A + B plus 1                                      |  |  |  |

|                                                                                                                                                         | L              | Н              | Ĺ              | L              | Ā∙B                           | $A + \overline{B}$                                        | A + B plus 1                                                  |  |  |  |

|                                                                                                                                                         | H              | H              | Ĺ              | L              | Logic "0"                     | minus 1 (2s comp.)                                        | Zero                                                          |  |  |  |

| C A <sub>0</sub> B <sub>0</sub> A <sub>1</sub> B <sub>1</sub> A <sub>2</sub> B <sub>2</sub> A <sub>3</sub> B <sub>3</sub>                               | L              | L              | H              | L              | Ā∙B                           | A plus (A ● B)                                            | A plus A • B plus 1                                           |  |  |  |

| C <sub>n</sub> 10 20 11 21 12 22 15 25 C <sub>n+4</sub> O-                                                                                              | Н              | L              | Н              | L              | B                             | $A \bullet \overline{B}$ plus $(A + B)$                   | A • B plus (A + B) plus                                       |  |  |  |

| M A=B                                                                                                                                                   | L              | Н              | Н              | L              | A ⊕ B                         | A minus B minus 1                                         | A minus B                                                     |  |  |  |

| <sup>30</sup> 'F181                                                                                                                                     | Н              | H              | H              | L              | A●B                           | A ● B minus 1                                             | A • B                                                         |  |  |  |

| <b>1</b> S₁ G <b></b>                                                                                                                                   | L              | L<br>L         | L<br>L         | Н              | Ā + B<br>Ā⊕B                  | A plus A • B                                              | A plus A • B plus 1                                           |  |  |  |

| - S <sub>2</sub>                                                                                                                                        | H<br>L         | H              | L              | H<br>H         | B<br>A⊕B                      | A plus B<br>A • B plus (A $+ \overline{B}$ )              | A plus B plus 1 A • B plus (A + B) plus                       |  |  |  |

| S <sub>3</sub> F <sub>0</sub> F <sub>1</sub> F <sub>2</sub> F <sub>3</sub>                                                                              | Н              | Н              | L              | Н              | A • B                         | A • B minus 1                                             | A • B plus (A + B) plus A • B                                 |  |  |  |

|                                                                                                                                                         | Ľ              | Ë              | H              | н              | Logic "1"                     | A plus A (2 × A)                                          | A plus A (2 × A) plus 1                                       |  |  |  |

| '''                                                                                                                                                     | H              | Ĺ              | Н              | Н              | $A + \overline{B}$            | A plus (A + B)                                            | A plus (A + B) plus 1                                         |  |  |  |

| b. All Input Data True                                                                                                                                  | L              | Н              | Н              | Н              | A + B                         | A plus (A $+ \overline{B}$ )                              | A plus (A + B) plus 1                                         |  |  |  |

|                                                                                                                                                         | Н              | Н              | Н              | Н              | Α                             | A minus 1                                                 | A                                                             |  |  |  |

|                                                                                                                                                         | L              | L              | L              | L              | _ Ā                           | A minus 1                                                 | A                                                             |  |  |  |

|                                                                                                                                                         | H              | L              | L              | L              | Ā + B                         | A ● B minus 1                                             | A • B                                                         |  |  |  |

| C <sub>n</sub> A <sub>0</sub> B <sub>0</sub> A <sub>1</sub> B <sub>1</sub> A <sub>2</sub> B <sub>2</sub> A <sub>3</sub> B <sub>3</sub> C <sub>n+4</sub> | L<br>H         | H<br>H         | L<br>L         | L<br>L         | Ā ● B<br>Logic "1"            | A • B minus 1                                             | A • B<br>Zero                                                 |  |  |  |

| - <b> </b> M                                                                                                                                            | L              | L              | Н              | L              | Logic I<br>•B                 | minus 1 (2s comp.)<br>A plus (A $+$ B)                    | A plus (A + B) plus 1                                         |  |  |  |

| - S <sub>0</sub> A=B                                                                                                                                    | H              | Ĺ              | н              | L              | В                             | A • B plus (A + B)                                        | A • B plus (A + B) plus                                       |  |  |  |

| -S <sub>1</sub> 'F181 G <b>O</b> -                                                                                                                      | L              | H              | Н              | L              | A ⊕ B                         | A plus B                                                  | A plus B plus 1                                               |  |  |  |

| S <sub>2</sub>                                                                                                                                          | Н              | Н              | Н              | L              | A + B                         | A + B                                                     | A + B plus 1                                                  |  |  |  |

| I PRO-I                                                                                                                                                 | L              | L              | L              | Н              | $\overline{A + B}$            | A plus (A $+ \overline{B}$ )                              | A plus (A + B) plus 1                                         |  |  |  |

| 0 1 2 3                                                                                                                                                 | H              | L              | L              | H              | A⊕B                           | A minus B minus 1                                         | A minus B                                                     |  |  |  |

| <del> </del>                                                                                                                                            | L              | Н              | L              | Н              | B                             | A ● B plus (A + B̄)                                       | A • B plus (A + B̄) plus                                      |  |  |  |

| c. A Input Data Inverted;                                                                                                                               | H<br>L         | H<br>L         | L<br>H         | H<br>H         | A + B<br>Logic "0"            | $A + \overline{B}$                                        | A + B plus 1                                                  |  |  |  |

| B Input Data True                                                                                                                                       | Н              | L              | Н              | Н              | Logic "0"<br>A • B            | A plus A (2 $\times$ A) A plus A $\bullet$ $\overline{B}$ | A plus A (2 $\times$ A) plus 1<br>A plus A $\bullet$ B plus 1 |  |  |  |

|                                                                                                                                                         | L              | Н              | Н              | Н              | A • B                         | A plus A ● B                                              | A plus A • B plus 1                                           |  |  |  |

|                                                                                                                                                         | H              | Н              | Н              | Н              | A                             | A                                                         | A plus 1                                                      |  |  |  |

|                                                                                                                                                         | L              | L              | L              | L              | Ā                             | A                                                         | A plus 1                                                      |  |  |  |

|                                                                                                                                                         | Н              | L              | L              | L              | Ā∙B                           | $A + \overline{B}$                                        | A + B plus 1                                                  |  |  |  |

| 19191919                                                                                                                                                | L              | Н              | L              | L              | $\overline{A + B}$            | A + B                                                     | A + B plus 1                                                  |  |  |  |

| C_ A <sub>0</sub> B <sub>0</sub> A <sub>1</sub> B <sub>1</sub> A <sub>2</sub> B <sub>2</sub> A <sub>3</sub> B <sub>3</sub>                              | H              | H              | L              | L              | Logic "0"                     | minus 1 (2s comp.)                                        | Zero                                                          |  |  |  |

| C <sub>n</sub> - No sq N   S   N 2 S 2 N 3 S C <sub>n+4</sub>   O -                                                                                     | L              | L              | Н              | L              | Ā + B                         | A plus A • B                                              | A plus A • B plus 1                                           |  |  |  |

| S- A=B                                                                                                                                                  | H<br>L         | L<br>H         | H<br>H         | L<br>L         | B<br>A ⊕ B                    | A ● B plus (A + B)<br>A plus B                            | A • B plus (A + B) plus<br>A plus B plus 1                    |  |  |  |

| s 'F181                                                                                                                                                 | Н              | Н              | Н              | L              | A ⊕ B                         | A plus B<br>A • B minus 1                                 | A plus B plus I<br>A • B                                      |  |  |  |

| ]°1                                                                                                                                                     | Ľ              | L              | L              | Н              | Ā∙B                           | A plus A • B                                              | A plus A • B plus 1                                           |  |  |  |

| S <sub>2</sub>                                                                                                                                          | H              | L              | Ĺ              | н              | A⊕B                           | A minus B minus 1                                         | A minus B                                                     |  |  |  |

| S <sub>3</sub> F <sub>0</sub> F <sub>1</sub> F <sub>2</sub> F <sub>3</sub>                                                                              | L              | Н              | Ĺ              | Н              | B                             | A • B plus (A + B)                                        | A • B plus (A + B) plus                                       |  |  |  |

|                                                                                                                                                         | Н              | Н              | L              | Н              | A●B                           | A ● B minus 1                                             | A•B                                                           |  |  |  |

| '''                                                                                                                                                     | L              | L              | Н              | Н              | Logic "1"                     | A plus A (2 ×_A)                                          | A plus A (2 × A) plus 1                                       |  |  |  |

| d. A Input Data True;                                                                                                                                   | Н              | L              | Н              | Н              | A + B                         | A plus $(A + \overline{B})$                               | A plus (A + B) plus 1                                         |  |  |  |

| B Input Date Inverted                                                                                                                                   | L              | Н              | Н              | Н              | $A + \overline{B}$            | A plus (A + B)                                            | A plus (A + B) plus 1                                         |  |  |  |

|                                                                                                                                                         | Н              | Н              | Н              | Н              | Α                             | A minus 1                                                 | A                                                             |  |  |  |

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{lll} \mbox{Storage Temperature} & -65^{\circ}\mbox{C to} + 150^{\circ}\mbox{C} \\ \mbox{Ambient Temperature under Bias} & -55^{\circ}\mbox{C to} + 125^{\circ}\mbox{C} \\ \mbox{Junction Temperature under Bias} & -55^{\circ}\mbox{C to} + 175^{\circ}\mbox{C} \\ \mbox{Plastic} & -55^{\circ}\mbox{C to} + 150^{\circ}\mbox{C} \\ \end{array}$

V<sub>CC</sub> Pin Potential to

Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V Input Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

Standard Output -0.5V to V<sub>CC</sub>

TRI-STATE® Output -0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated  $I_{OL}$  (mA) ESD Last Passing Voltage (Min) 4000V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

Free Air Ambient Temperature

Military  $-55^{\circ}\text{C to} + 125^{\circ}\text{C}$ Commercial  $0^{\circ}\text{C to} + 70^{\circ}\text{C}$

Supply Voltage

Military +4.5V to +5.5V Commercial +4.5V to +5.5V

### **DC Electrical Characteristics**

| Symbol           | Parameter                               |                                                                              | 54F/74F           |     |                              | Units | V <sub>CC</sub> | Conditions                                                                                                                                                                                                                                                                                                  |  |

|------------------|-----------------------------------------|------------------------------------------------------------------------------|-------------------|-----|------------------------------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syllibol         | Parame                                  | ter                                                                          | Min               | Тур | Max                          | Units | VCC             | Conditions                                                                                                                                                                                                                                                                                                  |  |

| V <sub>IH</sub>  | Input HIGH Voltage                      |                                                                              | 2.0               |     |                              | ٧     |                 | Recognized as a HIGH Signal                                                                                                                                                                                                                                                                                 |  |

| $V_{IL}$         | Input LOW Voltage                       |                                                                              |                   |     | 0.8                          | ٧     |                 | Recognized as a LOW Signal                                                                                                                                                                                                                                                                                  |  |

| $V_{CD}$         | Input Clamp Diode V                     | oltage                                                                       |                   |     | -1.2                         | ٧     | Min             | $I_{IN} = -18 \text{ mA}$                                                                                                                                                                                                                                                                                   |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                  | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.5<br>2.7 |     |                              | ٧     | Min             | $I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$                                                                                                                                                                                                                            |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                   | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub>                           |                   |     | 0.5<br>0.5                   | ٧     | Min             | $I_{OL} = 20 \text{ mA}$<br>$I_{OL} = 20 \text{ mA}$                                                                                                                                                                                                                                                        |  |

| l <sub>IH</sub>  | Input HIGH<br>Current                   | 54F<br>74F                                                                   |                   |     | 20.0<br>5.0                  | μΑ    | Max             | $V_{IN} = 2.7V$                                                                                                                                                                                                                                                                                             |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test    | 54F<br>74F                                                                   |                   |     | 100<br>7.0                   | μΑ    | Max             | $V_{IN} = 7.0V$                                                                                                                                                                                                                                                                                             |  |

| I <sub>CEX</sub> | Output HIGH<br>Leakage Current          | 54F<br>74F                                                                   |                   |     | 250<br>50                    | μΑ    | Max             | $V_{OUT} = V_{CC}(\overline{F}_n, \overline{G}, \overline{P}, C_{n+4})$                                                                                                                                                                                                                                     |  |

| V <sub>ID</sub>  | Input Leakage<br>Test                   | 74F                                                                          | 4.75              |     |                              | ٧     | 0.0             | $I_{ m ID}=$ 1.9 $\mu{ m A}$<br>All Other Pins Grounded                                                                                                                                                                                                                                                     |  |

| I <sub>OD</sub>  | Output Leakage<br>Circuit Current       | 74F                                                                          |                   |     | 3.75                         | μΑ    | 0.0             | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded                                                                                                                                                                                                                                                        |  |

| I <sub>IL</sub>  | Input LOW Current                       |                                                                              |                   |     | -0.6<br>-1.8<br>-2.4<br>-3.0 | mA    | Max             | $ \begin{aligned} &V_{ N} = 0.5V \text{ (M)} \\ &V_{ N} = 0.5V \text{ ($\overline{A}_0$, $\overline{A}_1$, $\overline{A}_3$, $\overline{B}_0$, $\overline{B}_1$, $\overline{B}_3$)} \\ &V_{ N} = 0.5V \text{ ($S_n$, $\overline{A}_2$, $\overline{B}_2$)} \\ &V_{ N} = 0.5V \text{ ($C_n$)} \end{aligned} $ |  |

| los              | Output Short-Circuit Current            |                                                                              | -60               |     | -150                         | mA    | Max             | $V_{OUT} = 0V (\overline{F}_n, \overline{G}, \overline{P}, C_{n+4})$                                                                                                                                                                                                                                        |  |

| I <sub>OHC</sub> | Open Collector, Output OFF Leakage Test |                                                                              |                   |     | 250                          | μΑ    | Min             | $V_O = V_{CC} (A = B)$                                                                                                                                                                                                                                                                                      |  |

| Icch             | Power Supply Current                    |                                                                              |                   | 43  | 65.0                         | mA    | Max             | V <sub>O</sub> = HIGH                                                                                                                                                                                                                                                                                       |  |

| I <sub>CCL</sub> | Power Supply Curren                     | t                                                                            |                   | 43  | 65.0                         | mA    | Max             | $V_O = LOW$                                                                                                                                                                                                                                                                                                 |  |

|                                      |                                                                            |      |            | 74F                                                                      |              | 5          | 4F                          | 7                                                                | 4F           |       |

|--------------------------------------|----------------------------------------------------------------------------|------|------------|--------------------------------------------------------------------------|--------------|------------|-----------------------------|------------------------------------------------------------------|--------------|-------|

| Symbol                               | Parameter                                                                  |      | V          | T <sub>A</sub> = +25°<br>C <sub>C</sub> = +5.0<br>C <sub>L</sub> = 50 pF | V            |            | <sub>C</sub> = Mil<br>50 pF | T <sub>A</sub> , V <sub>CC</sub> = Com<br>C <sub>L</sub> = 50 pF |              | Units |

|                                      | Path                                                                       | Mode | Min        | Тур                                                                      | Max          | Min        | Max                         | Min                                                              | Max          | =     |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay C <sub>n</sub> to C <sub>n + 4</sub>                     |      | 3.0<br>3.0 | 6.4<br>6.1                                                               | 8.5<br>8.0   | 3.0<br>3.0 | 10.0<br>9.5                 | 3.0<br>3.0                                                       | 9.5<br>9.0   | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{A}$ or $\overline{B}$ to $C_{n+4}$            | Sum  | 5.0<br>4.0 | 10.0<br>9.4                                                              | 13.0<br>12.0 | 5.0<br>3.5 | 15.5<br>16.5                | 5.0<br>4.0                                                       | 14.0<br>13.0 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{A}$ or $\overline{B}$ to $C_{n+4}$            | Dif  | 5.0<br>5.0 | 10.8<br>10.0                                                             | 14.0<br>13.0 | 5.0<br>4.0 | 17.0<br>15.0                | 5.0<br>5.0                                                       | 15.0<br>14.0 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $C_n$ to $\overline{F}$                                  | Any  | 3.0<br>3.0 | 6.7<br>6.5                                                               | 8.5<br>8.5   | 2.5<br>2.5 | 16.0<br>12.0                | 3.0<br>3.0                                                       | 9.5<br>9.5   | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $\overline{A}$ or $\overline{B}$ or $\overline{G}$       | Sum  | 3.0<br>3.0 | 5.7<br>5.8                                                               | 7.5<br>7.5   | 2.5<br>2.5 | 9.0<br>9.5                  | 3.0<br>3.0                                                       | 8.5<br>8.5   | ns    |

| t <sub>PLH</sub>                     | Propagation Delay $\overline{A}$ or $\overline{B}$ to $\overline{G}$       | Dif  | 3.0<br>3.0 | 6.5<br>7.3                                                               | 8.5<br>9.5   | 2.5<br>2.5 | 11.5<br>11.0                | 3.0<br>3.0                                                       | 9.5<br>10.5  | ns    |

| PLH<br>PHL                           | Propagation Delay $\overline{A}$ or $\overline{B}$ to $\overline{P}$       | Sum  | 3.0<br>3.0 | 5.0<br>5.5                                                               | 7.0<br>7.5   | 2.5<br>3.0 | 8.5<br>9.5                  | 3.0<br>3.0                                                       | 8.0<br>8.5   | ns    |

| PLH<br>PHL                           | Propagation Delay $\overline{A}$ or $\overline{B}$ to $\overline{P}$       | Dif  | 3.0<br>4.0 | 5.8<br>6.5                                                               | 7.5<br>8.5   | 2.5<br>3.0 | 11.0<br>11.0                | 3.0<br>4.0                                                       | 8.5<br>9.5   | ns    |

| PLH<br>PHL                           | Propagation Delay $\overline{A}_i$ or $\overline{B}_i$ to $\overline{F}_i$ | Sum  | 3.0<br>3.0 | 7.0<br>7.2                                                               | 9.0<br>10.0  | 3.0<br>3.0 | 14.5<br>14.5                | 3.0<br>3.0                                                       | 10.0<br>10.0 | ns    |

| PLH<br>PHL                           | Propagation Delay $\overline{A}_i$ or $\overline{B}_i$ to $\overline{F}_i$ | Dif  | 3.0<br>3.0 | 8.2<br>5.0                                                               | 11.0<br>11.0 | 3.0<br>3.0 | 17.5<br>14.5                | 3.0<br>3.0                                                       | 12.0<br>12.0 | ns    |

| PLH<br>PHL                           | Propagation Delay<br>Any A or B to Any F                                   | Sum  | 4.0<br>4.0 | 8.0<br>7.8                                                               | 10.5<br>10.0 | 3.5<br>4.0 | 16.5<br>13.5                | 4.0<br>4.0                                                       | 11.5<br>11.0 | ns    |

| PLH                                  | Propagation Delay                                                          | D:/  | 4.5        | 9.4                                                                      | 12.0         | 3.5        | 17.5                        | 4.5                                                              | 13.0         | ns    |

### **Ordering Information**

$\overline{\mathsf{A}}$  or  $\overline{\mathsf{B}}$  to  $\overline{\mathsf{F}}$

Any  $\overline{A}$  or  $\overline{B}$  to Any  $\overline{F}$

Propagation Delay

Propagation Delay

$\overline{A}$  or  $\overline{B}$  to A = B

$t_{PHL}$

$t_{PLH}$

$t_{\text{PHL}}$

$t_{\text{PLH}}$

$t_{PHL}$

Dif

Logic

Dif

3.5

4.0

4.0

11.0

6.0

9.4

6.0

6.0

18.5

9.8

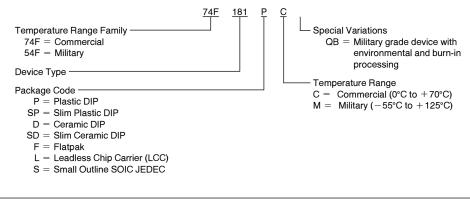

The device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows:

12.0

9.0

10.0

27.0

12.5

3.0

3.5

3.0

8.0

5.5

ns

ns

ns

13.0

10.0

11.0

29.0

13.5

3.5

4.0

4.0

11.0

6.0

14.0

14.5

15.5

35.0

21.0

### Physical Dimensions inches (millimeters) (Continued)

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86

Email: cnjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-532 93 58

Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.

# National Semiconductor was acquired by Texas Instruments.

http://www.ti.com/corp/docs/investor\_relations/pr\_09\_23\_2011\_national\_semiconductor.html

This file is the datasheet for the following electronic components:

74F181SPC - http://www.ti.com/product/74f181spc?HQS=TI-null-null-dscatalog-df-pf-null-wwe

74F181PC - http://www.ti.com/product/74f181pc?HQS=TI-null-null-dscatalog-df-pf-null-wwe