# **R&E** INTERNATIONAL, INC.

## **FEATURES**

- ♦ Two Independent Four-Bit Latches

- ♦ 3-State Outputs

- ♦ Direct Reset

- All Inputs Buffered

#### DESCRIPTION

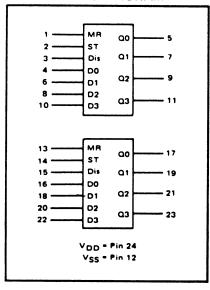

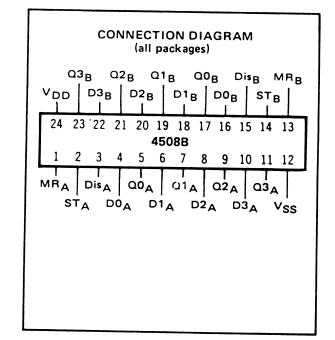

The 4508B consists of two identical independent 4-Bit Latches with separate Strobe (ST) and Master Reset (MR) controls. Separate Disable inputs force the outputs to a high-impedance state for bus line applications.

These devices find primary use in buffer storage, holding register, and display circuits, and other general digital logic applications.

#### **BLOCK DIAGRAM**

# **CMOS DUAL 4-BIT LATCH**

### TRUTH TABLE

| X        | X  | 1       | X  | X  | X  | X  | High Impedance |    |    |    |  |

|----------|----|---------|----|----|----|----|----------------|----|----|----|--|

| - !      | X  | 0       | X  | X  | Х  | X  | 0              | 0  | 0  | 0  |  |

| 0        | 0  | 00      | X  | X  | X  | X  | Latched        |    |    |    |  |

| 0        |    | 00      | 1  | 0  | 0  | 0  | 1              | 0  | 0  | 0  |  |

| 0        | 1  | 0       | 0  | 1  | 0  | 0  | 0              | 1  | 0  | 0  |  |

| 0        |    | 0       | 0  | 0  | 1  | 0  | 0              | 0  | 1  | 0  |  |

|          | 1  | 0       | 0  | 0  | 0  | 1  | 0              | 0  | 0  | 1  |  |

| <u> </u> | 1  | 0       | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  |  |

| MR       | ST | Disable | D3 | D2 | DI | DO | <b>Q</b> 3     | 02 | Q1 | 00 |  |

X = Don't Care

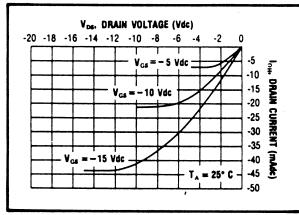

Typical P-Channel Source Current Characteristics

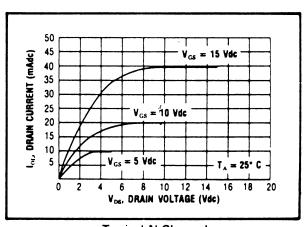

Typical N-Channel Sink Current Characteristics

# **ELECTRICAL CHARACTERISTICS**

# STATIC CHARACTERISTICS 1

| PARAMETER                      | V <sub>DD</sub> CONDITIONS | CONDITIONS    | ITIONS TLOW                                                                             | WC          | +25°C         |        |                    | THIGH         |             | Units             |      |

|--------------------------------|----------------------------|---------------|-----------------------------------------------------------------------------------------|-------------|---------------|--------|--------------------|---------------|-------------|-------------------|------|

|                                |                            | Min.          | Max.                                                                                    | Min.        | Тур.          | Max.   | Min.               | Max.          |             |                   |      |

| QUIESCENT DEVICE<br>CURRENT    | IDD                        | 5<br>10<br>15 | V <sub>IN</sub> = V <sub>SS</sub> or V <sub>DD</sub><br>All valid input<br>combinations | -<br>-<br>- | 5<br>10<br>20 | -<br>- | 0.05<br>0.1<br>0.2 | 5<br>10<br>20 | _<br>_<br>_ | 150<br>300<br>600 | μAdc |

| 3-STATE OUTPUT LEAKAGE CURRENT | IZL                        | 15            |                                                                                         | _           | ±0.1          | _      | ± 10 <sup>-4</sup> | ±0.1          | _           | ±1.0              | μAdc |

NOTES: 1 Remaining Static Electrical Characteristics are listed under "4000B Series Family Specifications".

# DYNAMIC CHARACTERISTICS (C<sub>L</sub> = 50pF, T<sub>A</sub> = 25°C)

| PARAMETER                                  | V <sub>DD</sub>                                                            | Min.           | Тур.        | Max.            | Units             |      |

|--------------------------------------------|----------------------------------------------------------------------------|----------------|-------------|-----------------|-------------------|------|

| PROPAGATION DELAY TIME<br>From Data Inputs | t <sub>РЦН</sub> , t <sub>РН</sub>                                         | 5<br>10<br>15  | -<br>-<br>- | 220<br>90<br>60 | 440<br>180<br>120 | ns   |

| From Disable Input                         | t <sub>PHZ</sub> , t <sub>PLZ</sub><br>t <sub>PZH</sub> , t <sub>PZL</sub> | 5<br>10<br>15  |             | 85<br>45<br>30  | 170<br>90<br>60   | ns   |

| OUTPUT TRANSITION TIME                     | t <sub>TLH</sub> , t <sub>THL</sub>                                        | 5<br>10<br>15  | _<br>_<br>_ | 100<br>50<br>40 | 200<br>100<br>80  | ns   |

| MINIMUM MASTER RESET PULSE WIDTH           | PW <sub>MR</sub>                                                           | 5<br>10<br>15  | _<br>_<br>_ | 100<br>50<br>35 | 200<br>100<br>70  | . ns |

| MINIMUM STROBE PULSE WIDTH                 | PW <sub>ST</sub>                                                           | 5<br>10<br>15  | -<br>-<br>- | 70<br>35<br>20  | 140<br>70<br>40   | ns   |

| MINIMUM SETUP TIME<br>Data Inputs          | t <sub>setup</sub>                                                         | 5<br>10<br>15  | -<br>-<br>- | 25<br>10<br>5   | 50<br>20<br>10    | ns   |

| MINIMUM HOLD TIME<br>Data Inputs           | t <sub>hold</sub>                                                          | 5<br>10ء<br>15 | ·           | 0 0             | , 0<br>0<br>0     | ns   |

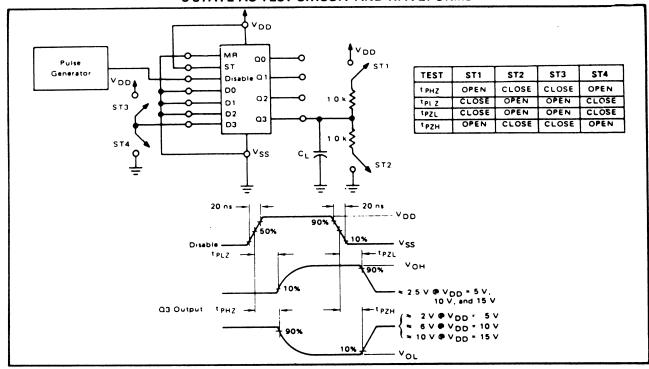

#### 3-STATE AC TEST CIRCUIT AND WAVEFORMS

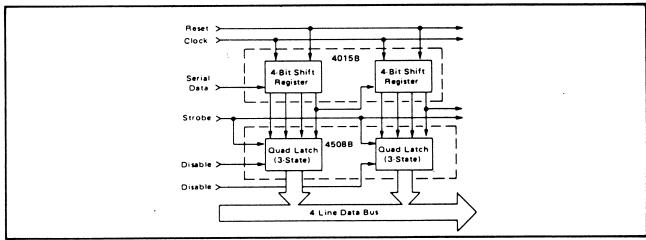

## APPLICATIONS INFORMATION

#### **BUS REGISTER**

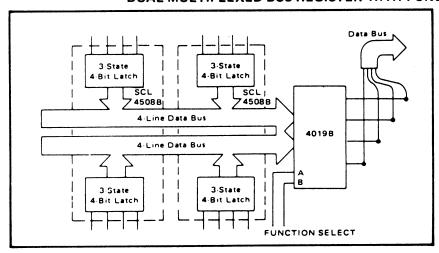

# DUAL MULTIPLEXED BUS REGISTER WITH FUNCTION SELECT

### **FUNCTION SELECT**

| Α |   | В | Function                        |

|---|---|---|---------------------------------|

| 0 | 4 | 0 | Inhibit (all 0)                 |

| 1 |   | 0 | Select A Bus                    |

| 0 |   | 1 | Select B Bus                    |

| 1 |   | 1 | A <sub>i</sub> + B <sub>i</sub> |